مسابقه طراحی مدارهای مجتمع خاصمنظوره

Direct Digital Synthesizer

هدف

موضوع انتخاب شده برای چالش ASIC طراحی یک سنتزکننده دیجیتال فرکانس است. شرکت کنندگان سختافزار مورد نیاز را طراحی، سنتز و در نهایت در سطح لیاوت پیادهسازی مینمایند و با ارائه طرح خود و گزارش مربوطه با هم به رقابت میپردازند. هدف از این مسابقه ارتقاء و ارزیابی توانمندی شرکتکنندگان در طراحی و پیادهسازی یک تراشه خاصمنظوره میباشد.

مقدمه

سنتز دیجیتال فرکانس روشی برای تولید شکل موجهای دلخواه با فرکانس و فاز قابل تنظیم در حوزه دیجیتال است که در آن از کلاک سیستم به عنوان مرجع فرکانس استفاده میشود. با پیشرفت تکنولوژی مدار مجتمع، سنتزکنندههای دیجیتال فرکانس (۱DDS) کاربردهای زیادی پیدا کردند که برخی از آنها عبارتند از: فانکشن ژنراتورهای آزمایشگاهی، گیرنده/فرستندههای رادیویی، رادار و حلقههای قفل فاز تمام دیجیتال. نسبت به سنتزکنندههای آنالوگ، مزایای زیر را میتوان برای DDS ها عنوان نمود:

- تنظیم بسیار دقیق فرکانس/فاز خروجی.

- امکان پرش لحظهای و بدون خطای گذرای فرکانس/فاز خروجی.

- تطبیق بسیار مطلوب مسیرهای I و Q در سنتزکنندههای متعامد.

- سازگاری با مدارات دیجیتال و انتقال سریعتر طراحی به تکنولوژیهای جدیدتر پیش رو.

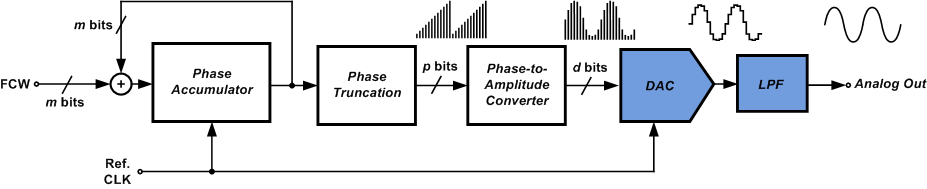

ساختار کلی یک DDS در شکل ۱ نشان داده شده است.

شکل ۱، ساختار کلی DDS. چالش ASIC انتخاب شده بلوکهای DAC و LPF را شامل نمیشود.

با توجه به ساختار نشان داده شده در شکل ۱، فرکانس خروجی \( f_0 \) توسط ورودی (FCW) Frequency Control Word و با توجه به رابطه زیر مشخص میشود:

\(f_0=f_{CLK} \times \frac{FCW}{2^m}\)

که در آن \( m \) تعداد بیتهای اکومولاتور فاز (بلوک Phase Accumulator) و \( f_{CLK} \) فرکانس کلاک مرجع است. معمولاً جهت تسهیل پیادهسازی بلوک تبدیل فاز به دامنه، تعدادی از بیتهای LSB مربوط به اکومولاتور فاز حذف میشود که این عملکرد توسط بلوک Phase Truncation در شکل ۱ نشان داده شده است. در یک پیادهسازی کامل، سیگنال دیجیتال تولید شده توسط بلوک DAC به سیگنال آنالوگ تبدیل میشود و در نهایت، یک فیلتر پایینگذر (فیلتر Anti Aliasing) هارمونیکهای فرکانس بالای شکل موج خروجی را حذف میکند. با توجه به اینکه هنگام تبدیل سیگنال دیجیتال به سیگنال آنالوگ، طیف سیگنال در مشخصه sinc ضرب میشود (اثر zero-order hold)، در بسیاری از پیادهسازیها این اثر به کمک یک فیلتر Inverse Sinc در حوزه دیجیتال جبرانسازی میشود تا دامنه سیگنال نهایی آنالوگ تولید شده به ازای تمام فرکانسها ثابت باشد. این ویژگی (یعنی ثابت ماندن دامنه سیگنال نهایی) در چالش انتخاب شده مد نظر میباشد. برای مطالعه بیشتر مباحث تئوری مورد نیاز شرکتکنندگان میتوانند به متن آموزشی خوبی که توسط Analog Devices ارائه شده (یا مراجع دیگر) مراجعه کنند.

تعریف مسأله

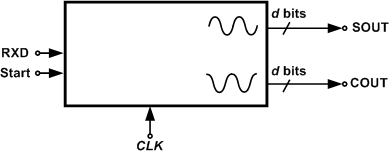

در این چالش، شرکتکنندگان یک DDS با ورودی/خروجیهای نشان داده شده در شکل ۲ طراحی میکنند. DDS طراحی شده دو خروجی سینوسی و کسینوسی (SOUT و COUT) خواهد داشت. تعداد بیتهای لازم برای این دو خروجی و همچنین فرکانس سیگنال کلاک توسط شرکتکنندگان مشخص میشود.

شکل ۲، DDS مورد نیاز.

مقدار FCW از طریق رابط UART (ورودی RXD) و دریافت پنج بایت قابل برنامهریزی است. مطابق شکل ۳، بایت دریافتی اول مربوط به ۸ بیت MSB خواهد بود و بایتهای بعدی به ترتیب سایر بیتهای FCW را مشخص میکنند. لازم به توضیح است، که با توجه به طراحی انجام شده و تعداد بیت لازم برای FCW، شرکت کنندگان از \( m \) بیت LSB برنامهریزی شده به عنوان FCW استفاده خواهند کرد.

![]() شکل ۳، ترتیب قرار گرفتن بایتهای دریافتی در رجیستر FCW.

شکل ۳، ترتیب قرار گرفتن بایتهای دریافتی در رجیستر FCW.

مشخصات رابط UART مورد نظر در جدول ۱ داده شده است.

جدول ۱، مشخصات رابط UART.

| ۱۱۵۲۰۰ | Baud Rate (bps) |

| ۸ | Data Bits |

| none | Parity |

| ۲ | Stop Bits |

| ۱ | Start Bit |

پس از برنامهریزی FCW و با لبه بالارونده ورودی Start، بلوک DDS شروع به تولید خروجیهای سینوسی و کسینوسی مینماید. محدودیتی در انتخاب معماری داخلی دلخواه برای پیادهسازی و استفاده از الگوریتمهای مناسب برای بهبود کیفیت سیگنال خروجی وجود ندارد. مشخصات مورد نظر برای DDS در جدول ۲ داده شده است.

جدول ۲، حداقل مشخصات مورد نیاز برای DDS.

| شماره | مشخصه | مقدار |

| ۱ | حداکثر فرکانس خروجی \( f_0 \) | \( > 50 \mathrm{~MHz} \) |

| ۲ | تفکیک فرکانس | \( < 1 \mathrm{~Hz} [/latex] |

| ۳ | اختلاف فاز دو خروجی (در بدترین حالت) | [latex] 90\pm 0.1^\circ \) |

| ۴ | حداکثر Spur (در بدترین حالت) | \( < -60 \mathrm{~dBc} [/latex] |

| ۵ | حداکثر تغییرات نسبی دامنه مؤلفه اصلی با تغییر فرکانس خروجی | [latex] 1 \% \) |

ابزارهای مورد نیاز جهت سنتز منطقی و فیزیکی و نیز کتابخانه طراحی مورد نیاز در مجموعه ابزارهای ICIC (فناوری ۱۸۰ نانومتر) که قبلاً در اختیار دانشگاهها قرار گرفته است، موجود هستند. مجموعه کل این ابزارها به همراه راهنمای نصب و استفاده از ابزارها، در قالب یک ماشین مجازی قابل نصب روی Windows توسط ICIC تهیه شده است و در دسترس عموم میباشد.

نحوه ارزیابی

شرط لازم برای وارد شدن طرحها به مسابقه، درستی عملکرد منطقی طرح و نیز برآورده کردن حداقل مشخصات خواسته شده در جدول ۲ است. همچنین کلیه طرحها باید در سطح Layout پیادهسازی شده باشند و DRC و LVS پاس شده باشد.

برای هر یک از طرحها، عملکرد DDS در هفت Setting فرکانسی آزمایش خواهد شد. برای هر آزمایش و پس از اعمال سیگنال Start، خروجیهای SOUT و COUT بعد از گذشت ده پالس کلاک و به تعداد مشخص نمونه مونیتور و ذخیره میشود. دیتای ذخیره شده با استفاده از کد متلبی که از پیش در اختیار شرکتکنندگان قرار داده خواهد شده ارزیابیمیشود و دامنه مؤلفه اصلی خروجیها ۲، اختلاف فاز آنها نسبت به هم، طیف خروجی و میزان حداکثر spur گزارش میشود. با ارزیابی نتایج هر هفت آزمایش، مشخصات DDS طراحی شده (به ویژه ردیفهای ۳ تا ۵ جدول ۲) برای هر طرح تعیین میگردد.

از میان طرحهای وارد شده به مسابقه، انتخاب طرحهای برگزیده با توجه به پارامترهای زیر صورت میپذیرد:

جدول ۳، پارامترهای ارزیابی.

| ردیف | پارامتر ارزیابی | حداقل امتیاز | حداکثر امتیاز | توضیحات |

| ۱ | گزارش طراحی (حداکثر ۴۰ صفحه) | ۰ | ۲۵ | متوسط امتیاز داده شده توسط داوران بر اساس کیفیت ظاهری، ساختار گزارش، کامل بودن ارائه روند طراحی و پیادهسازی، گزارشهای مربوط به نتایج تست. |

| ۲ | سطح تراشه | ۰ | ۱۵ | از رابطه \( \frac{Area_*}{Area}\times 15 \) محاسبه میشود؛ یعنی طرحی که کمترین سطح از تراشه را استفاده کرده، بیشترین نمره را کسب میکند و امتیاز سایر طرحها نسبت به بالاترین نمره نرمالیزه میشود. |

| ۳ | حداکثر فرکانس | ۰ | ۱۵ | از رابطه \( \frac{Freq}{Freq_*}\times 15 \) محاسبه میشود؛ یعنی طرحی که بالاترین فرکانس حداکثر را به دست آورده، بیشترین نمره را کسب میکند و امتیاز سایر طرحها نسبت به بالاترین نمره نرمالیزه میشود. |

| ۴ | توان مصرفی | ۰ | ۱۵ | از رابطه \( \frac{\frac{Freq}{Power}}{\left(\frac{Freq}{Power}\right)_*}\times 15 \) محاسبه میشود؛ یعنی طرحی که بالاترین نسبت فرکانس حداکثر به توان مصرفی را به دست آورده، بیشترین نمره را کسب میکند و امتیاز سایر طرحها نسبت به بالاترین نمره نرمالیزه میشود. |

| ۵ | تفکیک فرکانس | ۰ | ۱۵ | از رابطه \( 15-2\times \log_2\left(\frac{Res}{Res_*}\right) \) محاسبه میشود؛ یعنی طرحی که دقیقترین تفکیک فرکانس را به دست آورده، بیشترین نمره را کسب میکند و امتیاز سایر طرحها در مقایسه با بالاترین نمره محاسبه میشود. |

| ۶ | حداکثر Spur | ۰ | ۱۵ | از رابطه \( 15-\left(Spur-Spur_*\right) \) محاسبه میشود؛ یعنی بهترین رفتار Spur بالاترین نمره را کسب میکند و امتیاز سایر طرحها در مقایسه محاسبه میشود. |

فرکانسهای مورد تست

با توجه به اینکه تستها با کمک \(2^{20}\) نمونه انجام میشود، در تمام تستها \(m-20\) بیت LSB مربوط به FCW صفر در نظر گرفته میشود که باعث میشود تعداد \(2^{20}\) نمونه برای ارزیابی طراحی کافی باشد. همچنین بیت MSB در FCW همواره صفر خواهد بود تا فرکانس خروجی از فرکانس نایکوئیست کمتر باشد. با تغییر \( m-21 \) بیت باقیمانده، میتوان حالتهای تست را انتخاب نمود. در تست اول تمام بیتهای باقی مانده ۱ قرار داده میشود. در تست دوم مقدار دسیمال ۱ برای بیتهای باقیمانده قرار داده میشود و در تستهای سوم تا هفتم، مقادیر بیتهای باقیمانده به صورت تصادفی انتخاب خواهد شد.

برخی از فایلهای مورد نیاز

- تولید خروجیهای سینوسی و کسینوسی در Matlab: فایل dds_gen.m

- تست بنچ VHDL برای کدهای DDS: فایل testbench.vhd

- کد VHDL نمونه جهت استفاده در testbench و تولید خروجیهای سینوسی و کسینوسی: فایل DDS.vhd

- کد Matlab جهت ارزیابی خروجی تولید شده: فایل dds_eval.m

این فایلها را میتوانید به صورت یک فایل زیپ دانلود کنید.